這種方法在過去需要兩個獨立的開發團隊,這會增加非重復性工程成本、開發與技術風險。此外,該方法還將設計功能固定在處理器內核或可編程邏輯中,使后期優化難以進行。人們所需的開發工具應該可實現整個器件的軟件定義開發,并有能力根據需要將功能從處理器內核轉移到可編程邏輯,而且非HDL專家也能完成。這正是系統優化編譯器的用武之地。系統優化編譯器能利用C、C++或OpenCL?等高級語言以軟件方式定義整個系統行為。然后,使用系統優化編譯器執行處理器系統與可編程邏輯之前的功能分區,該編譯器能夠使功能無縫移動,以便選擇是在處理器系統中運行還是在可編程邏輯中實現。圖1-使用系統優化編譯器選擇要加速的功能。通過使用處理系統內部的內置定時器來為功能執行計時。

可找出造成瓶頸的功能,從而創建瓶頸功能。這些瓶頸功能便成為候選,以備通過使用系統優化編譯器在可編程邏輯中實現加速。處理系統與可編程邏輯之間的移動是通過系統優化編譯器的高層次綜合(可將C、C++、OpenCL程序轉換為Verilog或VHDL描述的工具)與軟件定義連接框架之間的結合來實現的。軟件定義連接框架能夠無縫地將HLS結果連接至軟件應用,設計團隊使用這種方法,一鍵就能在處理器和可編程邏輯間移動功能。當然在用戶把功能移動到可編程邏輯時,他們也得到了明顯的性能提升,自然這是使用可編程邏輯的結果。與CPU/GPU解決方案相比,在PL中進行加速還能提高確定性并降低時延,這對諸如ECU和ADAS的應用來說是至關重要的。

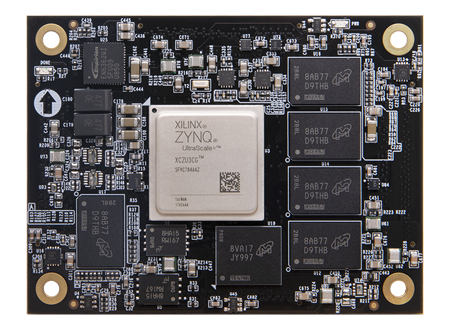

圖2-XC6SLX25T-3CSG324I 使用系統優化編譯器對資源與性能進行估算。很多汽車應用都是使用業界標準開源庫進行開發,例如在ADAS系統中使用OpenCV或Caffe,或在ECU中使用標準數學庫。為加快這些應用的開發,系統優化編譯器需要能夠支持多個HLS庫,以便開發人員在其應用中使用。系統優化編譯器應支持多個關鍵庫,·數學庫–提供標準數學庫的可綜合實現。·IP庫–為實現FFT、FIR和移位寄存器LUT功能提供IP庫。·線性代數庫–提供通用線性代數功能庫。·任意精度數據類型庫–使用有符號和無符號整數支持非2次冪的任意長度數據。該庫允許開發人員更高效地使用FPGA資源。這些庫的提供為開發團隊提供相當大的支持,讓開發團隊不必開發類似的功能。

EP3SL50F484C2N, XC4003E-3PQ100C, XC6VLX195T-2FFG784C,

EP3SL50F484I3N, XC4003E-4PC84C, XC6VLX195T-3FFG1156C,

EP3SL70F484I4, XC4005-4PQ160C, XC6VLX195T-L1FFG784I,

EP4C10F17C8N, XC4005-6PG156M, XC6VLX240T-1FF1156I,

EP4CE10E22C6N, XC4005E-3PQ100I, XC6VLX240T-1FF784I,

EP4CE10E22C8N, XC4005E-3TQ144C, XC6VLX240T-1FFG1156C,

EP4CE10E22C8N , XC4005E-4PC84C, XC6VLX240T-1FFG1156I,

EP4CE10E22I7, XC4005E-4PC84I, XC6VLX240T-1FFG1759C,

EP4CE10E22I7N, XC4005E-4PG156I, XC6VLX240T-1FFG1759I,

EP4CE10E22I8LN, XC4005E-4PG156M, XC6VLX240T-1FFG784C,

EP4CE10F17C6N, XC4005E-4PQ160I, XC6VLX240T-1FFG784I,

EP4CE10F17C7N, XC4005E-7TQ144C, XC6VLX240T-2FF1156C,

EP4CE10F17C8N, XC4005XL-2PQ100C, XC6VLX240T-2FF1156I,

EP4CE10F17C8N , XC4005XL-3PQ100C, XC6VLX240T-2FF1759I,

EP4CE10F17I7, XC4005XL-3TQ144C, XC6VLX240T-2FFG1156,

EP4CE10F17I7N, XC4006E-3PQ160C, XC6VLX240T-2FFG1156C,

EP4CE10F17I7N , XC4006E-3TQ144I, XC6VLX240T-2FFG1156I,

EP4CE10F17I8LN, XC4006E-4PQ160C, XC6VLX240T-2FFG1759I,

EP4CE10U14I7N, XC4006E-4PQ208I, XC6VLX365T-1FFG1156C,

EP4CE115F23C7N, XC4006E-4TQ144C, XC6VLX365T-1FFG1156I。