Xilinx Virtex-7 FPGA VC709 連接功能套件

產品描述

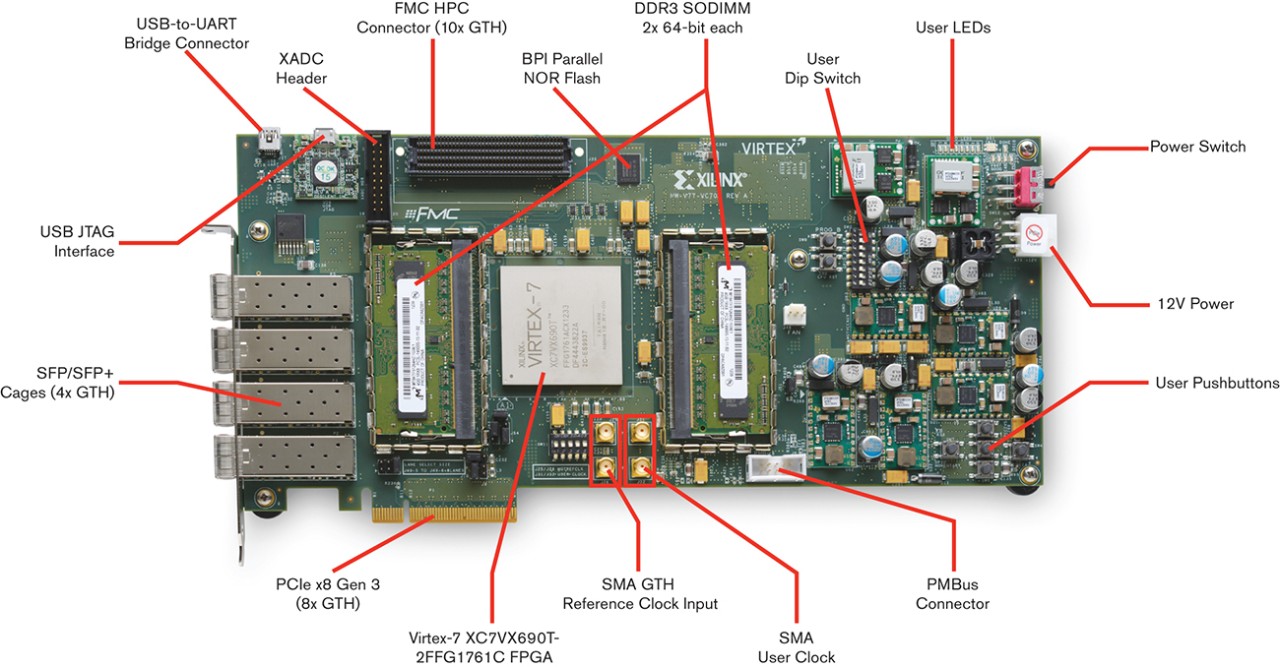

Virtex?-7 FPGA VC709 連接功能套件是一款速率為 40Gb/s 的高速平臺,您可以通過評估和開發連接功能,迅速為包含所有必要軟硬件和 IP 核的高帶寬和高性能應用提供強大的支持。它包括一個含有 PCI Express Gen 3、Northwest Logic 公司推出的 DMA IP 核、10GBase-R、AXI 以及與外部 DDR3 存儲器相連的虛擬 FIFO 存儲器控制器的 40Gb/s 目標參考設計。為了控制和監控此設計,本套件還包含一個在含有所有軟件驅動程序的 Fedora Live OS 基礎上構建的連接功能 GUI。此外,套件包含設計啟用的 2 個光纖電纜和 4 個收發器組件。

主要性能和優勢

使用 Virtex-7 VX690T FPGA ,實現面向高帶寬、高性能應用的 40Gb/s 連接功能平臺

硬件、設計工具、IP、以及預驗證參考設計

演示特色 10GBase-R 接口連接至外部 DDR3 存儲器

高級內存接口,可支持 2 個4GB DDR3 SODIM 內存, 速度可達 933MHz/1866Mbps。

實現與 PCIe Gen3x8、4 SFP+、SMA Pair 和 UART 的串行連接功能

支持包含 MicroBlaze、soft 32位 RISC 的嵌入式處理

開發網絡以及其它支持 4 SFP/SFP+ 端口的串行應用

擴展 I/O,包含 FPGA Mezzanine Card (FMC) 接口

電路板特性

包含 Xilinx Virtex-7 FPGA VC709 連接功能套件

時鐘技術

固定的振蕩器,帶有差分 200MHz 輸出

用作 FPGA “系統”時鐘

固定的振蕩器,帶有差分 233.33MHz 輸出

用作 “存儲器” 時鐘

用戶可編程 (IIC) 差分振蕩器 (范圍: 10MHz - 810 MHz、156.250 MHz 默認)

差分 SMA 時鐘輸入

差分 SMA GTH 參考時鐘輸入

抖動減弱時鐘

用于支持 CPRI/OBSAI 應用,從一個用戶提供的 SFP/SFP+模塊執行時鐘修復

通信與網絡

SFP/SFP+ 屏蔽罩 (4 個)

GTH 端口至FMC

UART 至 USB 的橋接器

PCI Express 8-通道邊緣連接器

存儲器

DDR3 SODIMM (2 個) - 各 4GB (最大 933MHz/1866Mbps)

BPI 并行 NOR 閃存: 32MB (256Mb)

IIC EEPROM: 1KB (8Kb)

配置

板上 JTAG 配置電路通過 USB 實現配置

BPI 并行 NOR 閃存: 32MB (256Mb)

擴展連接器

FMC-HPC (局部分布) 連接器

GTH 收發器 (x10) 、 160 個單端或 80 個差分 (34 LA & 46 HA) 用戶定義信號

VADJ 固定在 1.8 伏

控制 & I/O

個用戶按鈕開關 (x5)

用戶 DIP 開關 (8-位)

用戶 LED (x8)

功耗

AC 功耗適配器 (12V) 或 ATX

特色 Xilinx 器件

符合 ROHS 規范的 VC709 套件,包含 XC7VLX690T-FFG1761C

| 邏輯單元 | 693,120 |

|---|---|

| DSP slice | 3,600 |

| 內存 (Kb) | 52,920 |

| GTH 13.1 Gb/s 收發器 | 80 |

| I/O 引腳 | 1,000 |